CMOS(互補金屬氧化物半導體)集成電路在現代電子設備中發揮著核心作用,而邏輯門電路作為數字系統的基本構建塊,其分析與設計至關重要。同時,軟件開發在CMOS設計流程中扮演著不可或缺的角色,從仿真到自動化,軟件工具大大提升了設計效率和準確性。本文將探討CMOS邏輯門電路的基本分析方法和軟件開發在其中的應用。

一、CMOS邏輯門電路分析基礎

CMOS邏輯門電路以其低功耗、高噪聲容限和良好的可擴展性而著稱。分析CMOS邏輯門時,需關注以下關鍵方面:

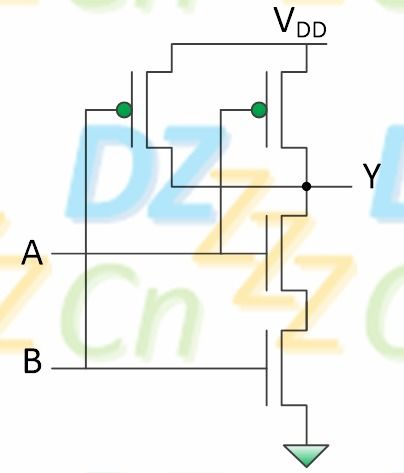

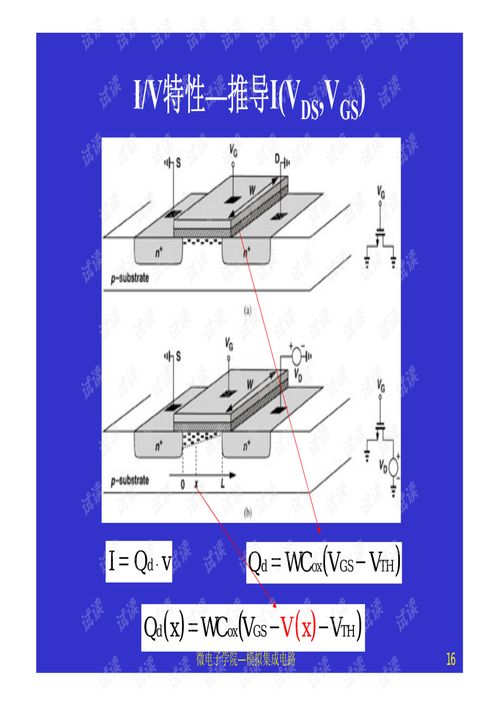

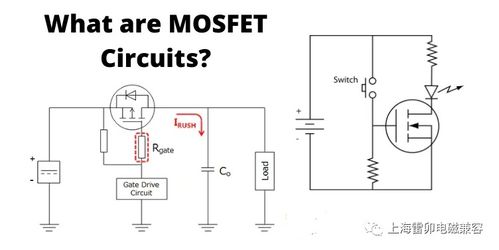

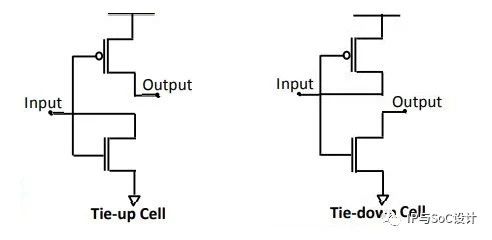

- 結構與工作原理:CMOS邏輯門由PMOS和NMOS晶體管互補組成,例如在反相器中,PMOS負責拉高輸出,NMOS負責拉低輸出。分析時需理解晶體管開關特性及其在邏輯狀態切換時的行為。

- 直流與交流分析:通過電壓傳輸特性(VTC)分析噪聲容限和邏輯電平;瞬態分析則評估延遲時間、上升/下降時間,這些參數直接影響電路速度。

- 功耗分析:靜態功耗幾乎為零,但動態功耗與開關頻率和負載電容相關,分析時需考慮電源電壓縮放和工藝變化的影響。

- 可靠性與縮放問題:隨著工藝節點縮小,分析需包括漏電流、熱效應和工藝變異對性能的影響。

二、軟件開發在CMOS邏輯門設計中的應用

軟件開發貫穿CMOS邏輯門電路的設計、驗證和優化全過程,主要工具和方法包括:

- 電路仿真軟件:使用SPICE(如HSPICE、LTspice)進行精確的電路行為仿真。開發者可以模擬邏輯門的瞬態響應、功耗和溫度效應,通過參數掃描優化晶體管尺寸。

- 硬件描述語言(HDL):VHDL或Verilog用于高級邏輯建模,結合仿真工具(如ModelSim)驗證功能正確性。這對于復雜邏輯門陣列的快速原型設計至關重要。

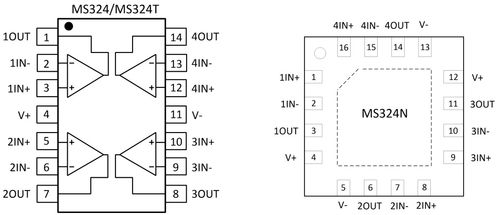

- 自動化設計工具:EDA(電子設計自動化)軟件,如Cadence Virtuoso或Synopsys Design Compiler,支持從原理圖輸入到布局生成的自動化流程。這些工具集成邏輯綜合、時序分析和物理設計,確保邏輯門滿足時序和面積約束。

- 定制腳本與算法:Python或Tcl腳本常用于自動化仿真和數據分析,例如批量測試不同工藝角下的邏輯門性能,或開發機器學習模型預測電路行為。

- 驗證與測試軟件開發:針對制造缺陷,開發測試模式生成軟件,確保邏輯門在硅片上的可靠性。

三、案例分析:反相器電路設計與軟件輔助

以CMOS反相器為例,設計過程首先通過手算確定W/L比以平衡上升/下降時間,然后使用SPICE仿真驗證VTC和延遲。軟件開發加速了這一過程:通過Python腳本自動調整參數并分析功耗-延遲乘積,最終在EDA工具中生成優化布局。

四、挑戰與未來趨勢

CMOS邏輯門分析面臨工藝縮放帶來的量子效應挑戰,而軟件開發需適應AI驅動的設計方法。未來,結合云計算和開源EDA工具,開發者可以更高效地實現復雜邏輯電路的分析與優化。

CMOS邏輯門電路分析與軟件開發相輔相成。深入理解電路原理,輔以先進的軟件工具,是推動集成電路創新和實現高性能、低功耗設計的關鍵。隨著技術演進,這一領域將繼續依賴跨學科協作,以應對日益復雜的電子系統需求。